# Introduction to the iAPX 286

intel

ORDER NUMBER: 210308-001 AFN-02177A

## inte

## Introduction to the iAPX 286

February 1982

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

BXP, CREDIT, i, ICE, iCS, i<sub>m</sub>, iMMX, Insite, Intel, int<sub>e</sub>l, Intelevision, Intellec, iOSP, iRMX, iSBC, iSBX, Library Manager, MCS, Megachassis, Micromainframe, Micromap, Multimodule, Plug-A-Bubble, PROMPT, RMX/80, System 2000 and UPI.

MDS is an ordering code only and is not used as a product name or trademark. MDS<sup>®</sup> is a registered trademark of Mohawk Data Sciences Corporation.

\* MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Department SV3-3 3065 Bowers Avenue Santa Clara, CA 95051

### **TABLE OF CONTENTS**

| SECTION 1<br>INTRODUCTION                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SECTION 2<br>MANAGEMENT OVERVIEW OF THE IAPX 286                                                                                                                                                            |

| Summary of iAPX 286 Benefits                                                                                                                                                                                |

| iAPX 286 Addresses Application RequirementsProtection of Software Investments2-3Increased Throughput2-3Product Flexibility and Upgradability2-4New Architecture for Simplified Software Development2-5      |

| Flexible Hardware Configurations       2-6         Numeric Data Processor       2-6         Multiprocessor Capabilities       2-6         System Support Circuits       2-7         Board Systems       2-7 |

| Sample ApplicationsiAPX 86 System Upgrade2-7Multi-user Systems2-8Real-time Multitasking Systems2-8Multiprocessor Systems2-8Real-time High-performance Systems2-8                                            |

| Development Systems and SoftwareIntellec™ Microcomputer Development Systems2-9Evaluation Software2-9Development Software2-9High-level Languages2-9                                                          |

| Summary                                                                                                                                                                                                     |

|                                                                                                                                                                                                             |

#### SECTION 3 TECHNICAL OVERVIEW OF THE IAPX 286

#### **Basic Programming Model**

| Basic Register Model            | -1 |

|---------------------------------|----|

| Basic Data Types                | -3 |

| Basic Addressing Modes          |    |

| Direct Addressing               | -4 |

| Indirect Addressing             |    |

| Register Indirect Addressing 3- | -5 |

| Based or Indexed Addressing 3-  | -6 |

| Based Indexed Addressing 3-     | -7 |

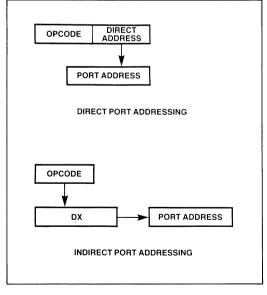

| String Addressing.       I/O Port Addressing .         I/O Port Addressing .       Address Mode Summary.         Flag Operations .       Basic Instruction Set .         Basic Instruction Set .       General-purpose Data Transfers .         General-purpose Data Transfers .       General-purpose Data Transfers .         Arithmetic Instructions .       General-purpose Data Transfers .         Flag Instructions .       General-purpose Data Transfers .         Arithmetic Instructions .       General-purpose Data Transfers .         String Instructions .       General-purpose Data Transfers .         String Operations .       General-purpose Data Transfers .         String Operations .       General-purpose Data Transfer .         Control Transfer Instructions .       General-purpose Data Transfer Instructions .         String Operations .       General-purpose Data Transfer Instructions .         Conditional Transfer Instructions .       General-purpose Data Transfer Instructions .         Unconditional Transfer Instructions .       General-purpose Data Transfer .         Block I/O Instructions .       General-purpose Data Transfer .         Block I/O Instructions .       General-purpose .         Translate Instruction .       General-purpose .         Array Bounds Check Instruction .       General-purpose .         General-purpose . | 3-8<br>3-9<br>3-9<br>3-9<br>3-9<br>-10<br>-11<br>-11<br>-11<br>-12<br>-12<br>-13<br>-13<br>-13<br>-13<br>-13 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Extended Capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                              |

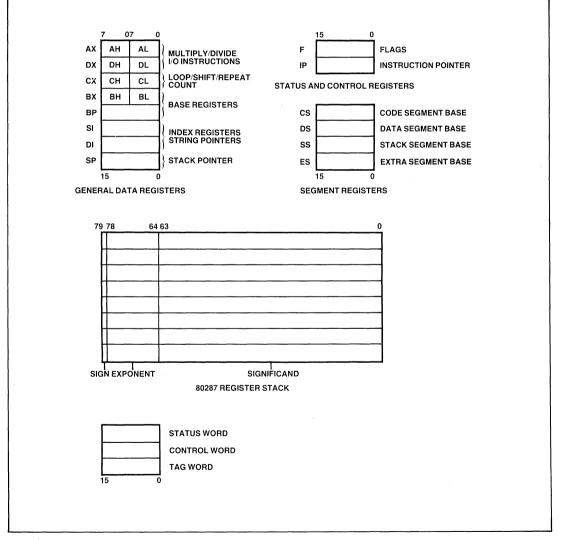

| Extended Register Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -15                                                                                                          |

| Extended Data Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -15                                                                                                          |

| Integer Data Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -15                                                                                                          |

| Floating-point Data Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

| Packed BCD Data Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |

| Extended Addressing Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

| Extended Numeric Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                              |

| Arithmetic Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                              |

| Comparison Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                              |

| Transcendental Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                              |

| Data Transfer Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                              |

| Constant Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                              |

| Advanced Programming Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17                                                                                                           |

| Segmentation of Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -17                                                                                                          |

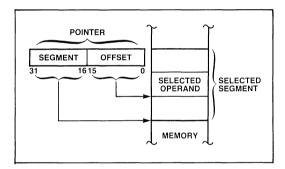

| Pointer Data Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              |

| Segment Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                              |

| Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                              |

| Two Modes: Real Address and Protected Virtual Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                              |

| Protected Virtual Address Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -21                                                                                                          |

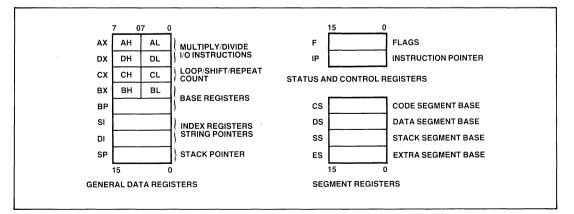

Full Register Set

3-22

Segment Registers in Protected Virtual Address Mode

3-22

#### APPENDIX A iAPX 286 INSTRUCTIONS

| Data Transfer Instructions            |   |

|---------------------------------------|---|

| General-purpose Data TransfersA-      |   |

| Accumulator-specific TransfersA-      |   |

| Address Transfers                     | 1 |

| Flag Register Transfers               | 2 |

| Arithmetic Instructions               | 2 |

| Addition Instructions                 |   |

| Subtraction Instructions              |   |

| Aultiplication Instructions           |   |

| Division Instructions                 |   |

|                                       | , |

| ogic InstructionsA-4                  | 1 |

| String Instructions                   | 5 |

| Control Transfer Instructions         | 5 |

| Conditional Transfer Instructions     |   |

| Jnconditional Transfer Instructions   |   |

| teration Control Instructions         |   |

| Flag Operations                       |   |

|                                       |   |

| nterrupt InstructionsA-7              | , |

| Procedure Implementation Instructions | 3 |

| Protected Virtual Address Mode Instructions | A-9 |

|---------------------------------------------|-----|

| APPENDIX B<br>GLOSSARY                      | B-1 |

| APPENDIX C<br>SAMPLE INSTRUCTION TIMINGS    | C-1 |

## LIST OF FIGURES AND TABLES

#### FIGURE NUMBER FIGURE NAME

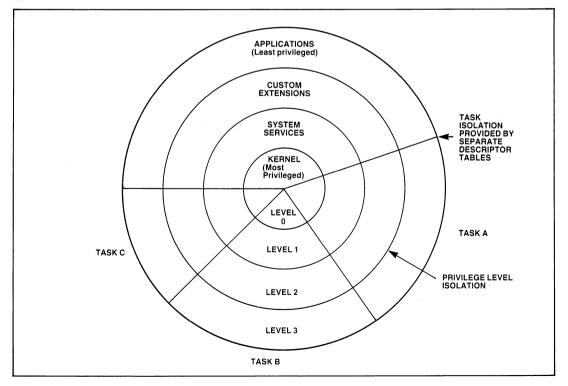

| 2-1   | Four Levels of Protection                             | 2-2  |

|-------|-------------------------------------------------------|------|

| 2-2   | iAPX 286 Performance Comparison                       | 2-3  |

| 2-3   | Concurrent Processing Enhances Speed                  | 2-4  |

| 3-1   | Address Space of Real Address Mode and                |      |

|       | Protected Virtual Address Mode                        |      |

| 3-2   | Program Registers of the Base Architecture            | 3-3  |

| 3-3   | Immediate Addressing                                  |      |

| 3-4   | Register Addressing                                   | 3-4  |

| 3-5   | Direct Addressing.                                    | 3-4  |

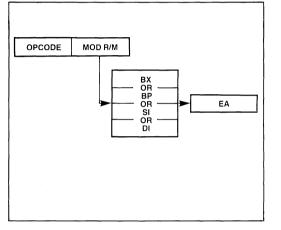

| 3-6   | Register Indirect Addressing.                         | 3-5  |

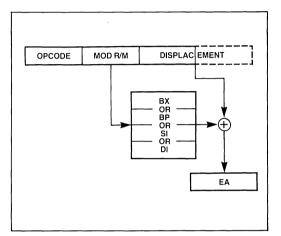

| 3-7   | Based Addressing                                      | 3-5  |

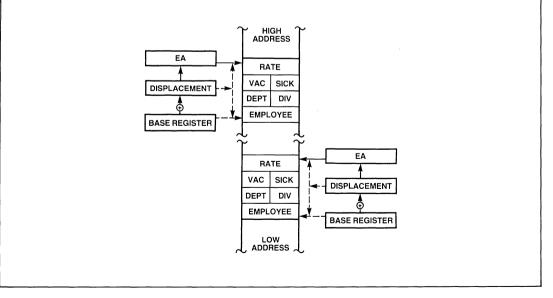

| 3-8   | Accessing a Structure with Based Addressing           | 3-5  |

| 3-9   | Indexed Addressing                                    | 3-6  |

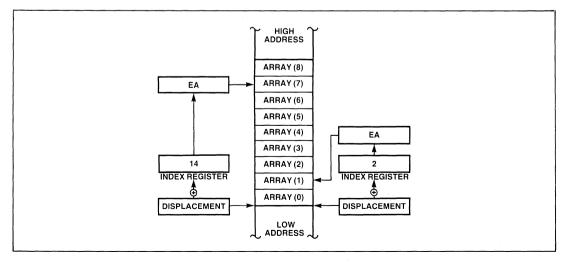

| 3-10  | Accessing an Array with Indexed Addressing            | 3-6  |

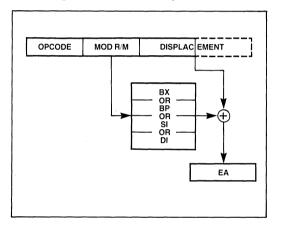

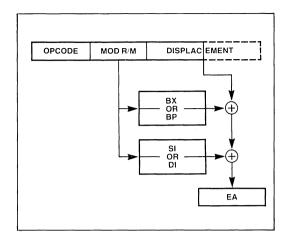

| 3-11  | Based Indexed Addressing.                             | 3-7  |

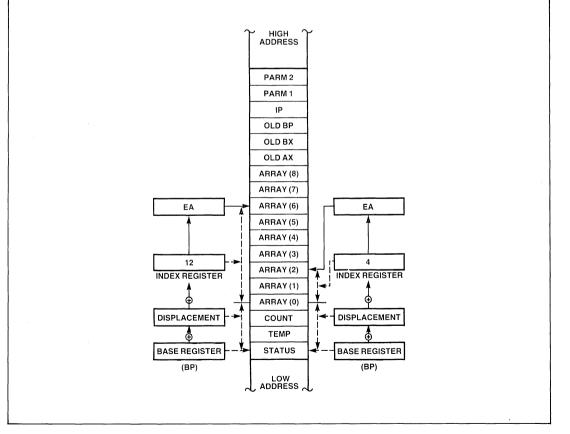

| 3-12  | Accessing a Stack Array with Based Indexed Addressing | 3-7  |

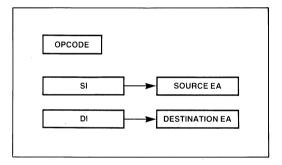

| 3-13  | String Addressing.                                    | 3-8  |

| 3-14  | I/O Port Addressing                                   | 3-8  |

| 3-15  | Extended Register Set                                 | 3-14 |

| 3-16  | Extended Data Types                                   | 3-16 |

| 3-17  | Address Pointer                                       | 3-19 |

| 3-18  | Advanced Register Set                                 | 3-19 |

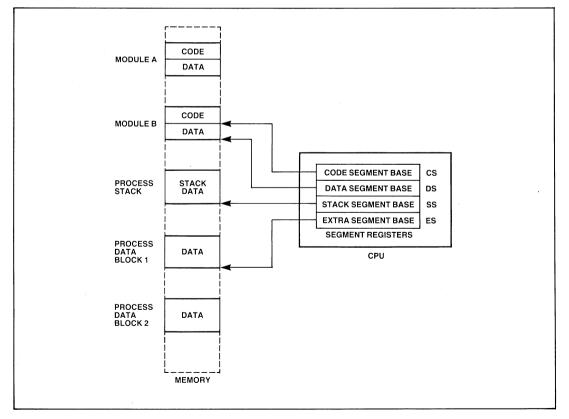

| 3-19  | Segmented Memory Helps Structure Software             |      |

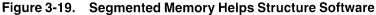

| 3-20  | iAPX 86 Real Address Mode Address Calculation         | 3-21 |

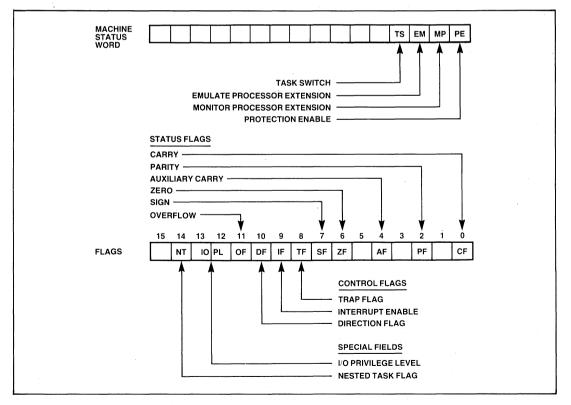

| 3-21a | Full Register Set                                     | 3-23 |

| 3-21b | Flags and Machine Status Word Bit Functions           | 3-24 |

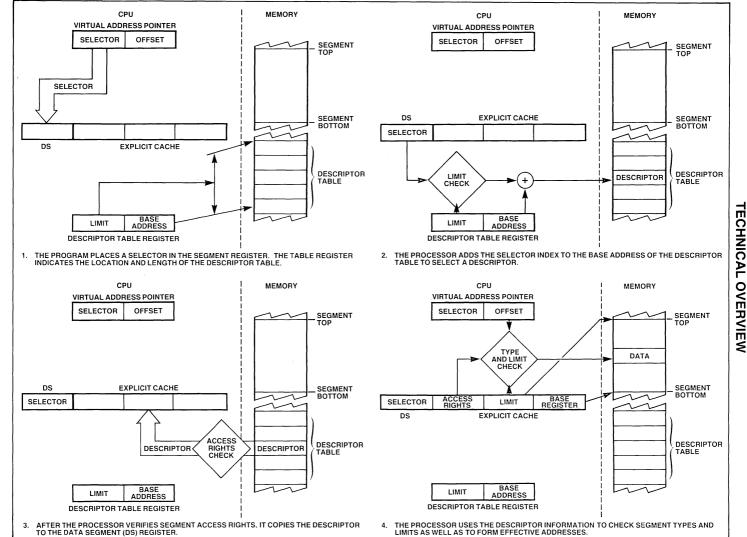

| 3-22  | Loading the Explicit Cache                            | 3-25 |

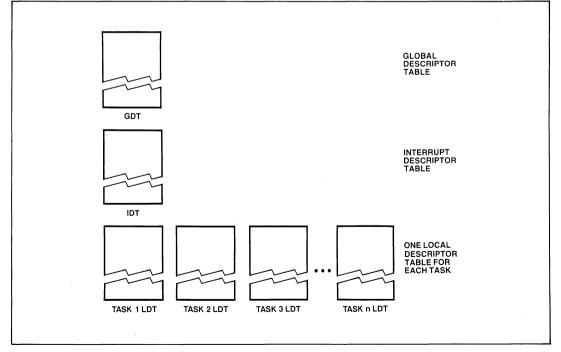

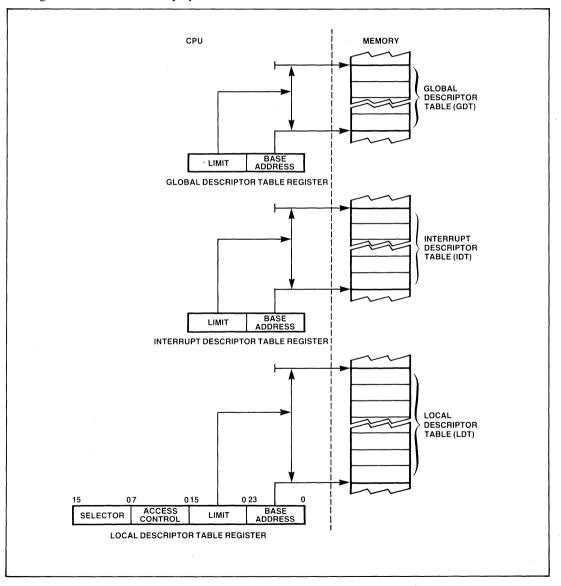

| 3-23  | Descriptor Tables                                     | 3-26 |

| 3-24  | Descriptor Table Registers                            | 3-27 |

| 3-25  | Four Privilege Levels                                 | 3-29 |

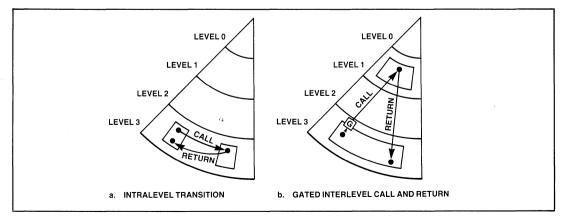

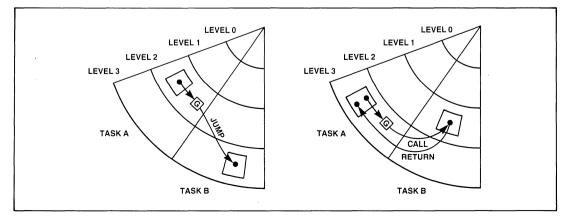

| 3-26  | Control Transfers Within a Task                       |      |

| 3-27  | Control Transfers Between Tasks                       | 3-31 |

| 3-28  | Virtual Memory Operation                              | 3-33 |

| 3-29  | Numeric Data Processor Configuration.                 |      |

| 3-30  | Multibus/Multiprocessor Configuration                 |      |

|       |                                                       |      |

##

#### NUMBER TABLE NAME

| A-1 | Interpretation of Conditional TransfersA | ۰-6 |

|-----|------------------------------------------|-----|

| A-2 | Predefined Interrupt VectorsA            | ۰-7 |

ł

## Section 1 Introduction

!

1

#### SECTION 1 INTRODUCTION

The iAPX 286 is a new VLSI microprocessor system with exceptional capabilities for supporting large-system applications. Based on a newgeneration CPU (the Intel 80286), this powerful microsystem is designed to support multi-user reprogrammable and real-time multitasking applications. Its dedicated system support circuits simplify system hardware; sophisticated hardware and software tools reduce both the time and the cost of product development.

The iAPX 286 microsystem is a total-solution approach that enables you to develop highspeed, interactive, multi-user, multitasking and multiprocessor—systems more rapidly and at costs lower than ever before.

- Reliability and system "up-time" are becoming increasingly important in all applications. Information must be protected from misuse or accidental loss. The iAPX 286 includes a protection mechanism that continually monitors application and operating system programs to maintain a high degree of system integrity.

- The iAPX 286 provides a large address space to support today's application requirements. Real memory consists of up to 16 megabytes (2<sup>24</sup> bytes) of RAM or ROM. This large physical memory enables the iAPX 286 to keep many large programs and data structures in memory simultaneously for high-speed access.

- For applications with dynamically changing memory requirements such as multi-user business systems, the iAPX 286 CPU provides onchip memory management and even virtual memory support. On an iAPX 286-based system, each user can have up to a gigabyte (2<sup>30</sup> bytes) of virtual address space. This large address space virtually eliminates restrictions

on the number or size of programs which may be part of the system.

• Large multi-user or real-time multitasking applications can use the advanced features and high-speed operation of the iAPX 286 to reduce response time for system users. Microcomputer systems servicing four or five simultaneous users may now be expanded to support more than three times that number, and real-time systems can respond in one-sixth the time or less.

The iAPX 286 is instruction-set-compatible with the iAPX 86 and the iAPX 88, ensuring that your investments in existing iAPX 86 software are well protected. This software, as well as an extensive base of third party software written for the iAPX 86 and 88, may be executed as-is on the iAPX 286 to take advantage of its much higher performance.

Upgrading iAPX 86 and 88 application programs to use the new memory management and protection features of the iAPX 286 usually requires only reassembly or recompilation. (Some programs may require minor modification.) This compatibility, along with strong system support from Intel, reduces both the time and the cost of software development. You can bring new products to market quickly.

This Introduction to the iAPX 286 describes the features and capabilities of the iAPX 286 microsystem. Section 2, directed to management, gives an overview of iAPX 286 capabilities. Section 3 is directed to the system designer. It discusses the features of the iAPX 286 in greater detail to provide a working knowledge of its operation. A glossary is included at the end of the manual to define terminology describing the operation of the iAPX 286.

## Section 2 Management Overview of the iAPX 286

Z

#### SECTION 2 MANAGEMENT OVERVIEW OF THE iAPX 286

Intel's iAPX 286 microsystem provides the most capable and cost-effective solution for your products. Memory protection, virtual memory, and high throughput rates promote the design of reliable multi-user and multitasking system products.

The iAPX 286 is also software-compatible with the world-standard iAPX 86 and 88 microprocessors—you can take advantage of a rapidly growing base of applications software to support your products.

The complete family of support circuits simplifies creation of hardware systems. Development support tools from Intel also aid the designer in creating system hardware and software.

The iAPX 286 includes many features which provide greater capability, reliability, and throughput than previously available with microprocessors. These features address the needs of your markets in three key ways:

- 1. iAPX 286 memory protection provides superior system reliability—a requirement for multi-user and multitasking systems.

- 2. Built-in support for memory management and virtual memory allows you to build flexible and cost-effective systems, and build them faster at less cost. The iAPX 286 enables a system designer to use these features in a variety of ways to best fit the target application.

- 3. Applications software already written for the iAPX 86 and 88 can be used to put iAPX 286 systems to work immediately.

#### SUMMARY OF iAPX 286 BENEFITS

Greater reliability—An innovative totalprotection system not only isolates the operating system from application programs, but also protects application programs and data from other programs. This protection gives unparalleled software integrity and up-time in a microprocessor-based system.

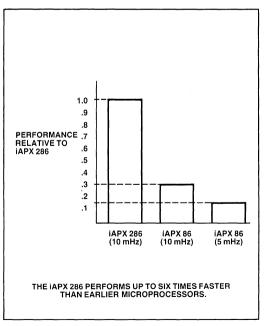

Higher performance—The iAPX 286 can execute instructions up to six times faster than the iAPX 86. As a result, new features and capabilities can be included in your product.

Protection of software investment—Operating in Real Address Mode, the iAPX 286 can use unmodified programs from the iAPX 86 and 88, while providing up to a six-fold increase in performance over these processors. This compatibility lets you use existing software to develop more powerful iAPX 286-based products. Newer software may then take advantage of the advanced iAPX 286 features available in Protected Virtual Address Mode. A major iAPX 286 advantage is that the designer can add these enhanced features at any time to an iAPX 286based product without hardware modification.

More software flexibility—Users may customize an operating system without compromising its integrity. Additionally, the architecture and instruction set can be customized to the system needs using CPU extension devices which add new capabilities like high-speed floating-point arithmetic.

Increased data access—The iAPX 286 supports a 16-megabyte real memory space able to contain many programs and data files simultaneously for immediate access. The iAPX 286 can also provide as much as a gigabyte (2<sup>30</sup> bytes) of virtual memory space per user for even greater programming flexibility.

Decreased development costs—The features of the iAPX 286 and the system development tools from Intel reduce the time required to develop new products. Intel provides a complete set of hardware and software development tools including high-level languages, single-board computers, in-circuit emulators, and networked development systems to drastically reduce the time and cost of product development. The extensive iAPX 286 family of support circuits, memories, and peripheral control circuits reduces the complexity of hardware design.

#### iAPX 286 ADDRESSES APPLICATION REQUIREMENTS

The iAPX 286 extends the capabilities of the iAPX 86 and 88 processors to increase the power and simplify the development of multi-user and multitasking systems. The iAPX 286 directly addresses the needs of these systems by increasing address space, reducing system response time, increasing system reliability, and reducing software development costs.

System Reliability and Data Integrity—Never before has there been a microprocessor with such extensive and flexible software protection features to keep systems up and running and to keep data protected. For any application, a system designer can structure the protection mechanism to match the requirements of the product.

- Task isolation—All tasks are completely isolated from interference by other tasks. As a result, users of an iAPX 286-based protected computer system do not have to worry about another user crashing the system or violating the integrity of their programs and data.

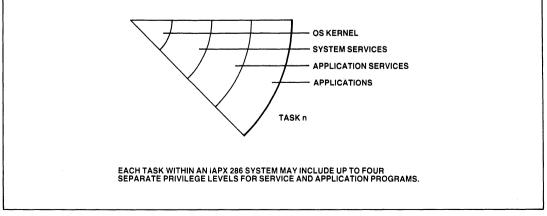

- Operating system protection—The iAPX 286 protection mechanism provides up to four privilege levels within each task (see Figure 2-1). The highest privilege level is reserved for the operating system kernel, the most trusted program in the system. Below the kernel level, systems can be configured to include a system service level, an application program level. These hierarchical privilege levels encourage structured operating systems simpler to implement and easier to maintain.

- Controlled operating system access—The transparent operation of the iAPX 286 protection mechanism saves the programmer from writing special instructions to request operating system services. Quick but well-controlled access from an application program to operating system service routines preserves the integrity of the operating system as well as the high-speed attributes of the CPU.

Figure 2-1. Four Levels of Protection

#### Protection of Software Investments

Software is rapidly becoming the largest investment in any computer system. The iAPX 286 protects both current and future investments in software. It offers two modes of operation which are fully upward compatible with software developed for the iAPX 86 and 88 processors. This feature not only benefits current iAPX 86 and 88 users, but it also allows customers to select from the large base of existing thirdparty software. Compatibility also extends to include iAPX 86/20, 88/20 Numeric Data Processor systems using the 80287 Numeric Processor extension.

Real Address Mode makes the iAPX 286 appear exactly like an iAPX 86, while executing as much as six times faster. This mode can provide a major savings in software development costs by enabling you to use programs developed for the iAPX 86 and 88 without any modification.

Figure 2.2 iAPX 286 Performance Comparison

Protected Virtual Address Mode (Protected Mode) lets you take advantage of memory management and protection features easily. Protected Mode is used for the highest product reliability, data integrity, and largest address space. This mode also makes it efficient to use the existing iAPX 86 and 88 software.

Application programs developed for the iAPX 86 require little or no modification to use Protected Mode. High-level language application programs only need to be recompiled, while some assembly language programs may require minimal modifications. Because most application programs do not require modification to run on the iAPX 286, the user is assured that this microsystem preserves the original integrity of proven software.

The iAPX 286 completely supports the iAPX 86 instruction set in Protected Mode as well as in Real Address Mode. Intel's commitment to protect software investments continues with the iAPX 286.

#### **Increased Throughput**

State-of-the-art Very Large Scale Integration (VLSI) techniques enable the iAPX 286 to execute programs up to six times faster than previous-generation 16-bit microprocessors (see Figure 2-2).

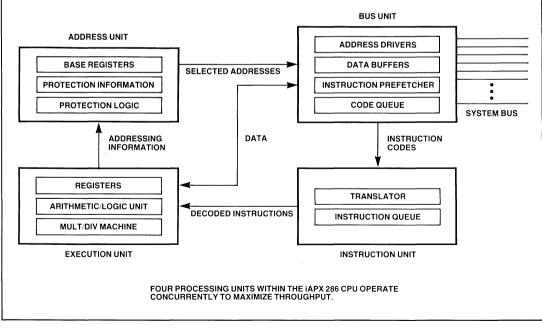

Four processing units—A major performance innovation in the iAPX 286 design is the implementation of four independent processing units within the Central Processing Unit (CPU) (see Figure 2-3). Each independent unit operates to minimize bus requirements and to maximize CPU throughput. The iAPX 286 will be available in both 8-megaHertz and 10-megaHertz versions.

High-performance bus—iAPX 286 design combines a new demultiplexed bus structure with pipelining techniques to more than double bus efficiency. This increased bus efficiency maximizes the information-handling capacity of the system for greater performance. Pipelined bus operation achieves this higher bus throughput without requiring proportional increases in memory speed. The high-performance bus interface and a 10-megaHertz clock rate provide a bus bandwidth of 10 megabytes per second.

## Product Flexibility and Upgradability

The iAPX 286 can address up to 16 megabytes of physical memory. Built-in iAPX 286 virtual memory management support hardware can make a much larger address space available to accommodate even more programs and data. This flexible address space allows you to build products which are easy to upgrade to include new features and capabilities.

This on-chip virtual memory management support enables a system to allocate as much as a

gigabyte  $(2^{30}$  bytes) of virtual address space to each user. Virtual memory eliminates the problems associated with limited address space. The large address space enables programmers to concentrate their efforts on improving program operation, rather than on designing programs around address space restrictions.

The large physical address space and built-in virtual memory support are ideal for implementing multi-user reprogrammable systems. The number of programs, the size of data bases, and the number of users in the system are not constrained by the size of physical memory.

The operation of the on-chip iAPX 286 memory management unit is transparent and requires no special instructions for its use. Because this memory management support is integral to the CPU, systems based on the iAPX 286 operate faster, are easier to program, and require less hardware and software than systems requiring an external memory management unit.

Figure 2-3. Concurrent Processing Enhances Speed

Hardware support for system operations—The iAPX 286 also supports high-speed system operation with specialized on-chip hardware:

- The 16-bit multiply and divide instructions of the iAPX 286 operate more than ten times faster than those of the iAPX 86 and 88. Special instructions for string handling and highlevel languages further enhance system performance.

- Multitasking support hardware reduces to less than 18 microseconds the time required to switch processing from one task or user to another. The code requirements for this switch are eliminated because this hardware automatically performs the operations of suspending one program, saving registers, restoring registers, and continuing with another program.

- The processor's high-speed interrupt-handling hardware enables the system to respond quickly to an external event. An iAPX 286 system is capable of responding to an interrupt in less than 3 microseconds.

- Other on-chip hardware simplifies the implementation and speeds the operation of operating system functions such as virtual memory management and memory protection.

Advanced numeric processing—The basic iAPX 286/10 configuration (an 80286 CPU and support circuits) may be expanded to an iAPX 286/20 Numeric Data Processor configuration. This configuration handles number-crunching applications which use up to 64-bit integer or 80-bit floating-point data types. It includes a processor extension that operates concurrently with the 80286 CPU, handling arithmetic calculations up to 100 times faster than comparable software. The iAPX 286/20 configuration conforms to the proposed IEEE Standard P754 for numeric processing.

In summary, the hardware of the 80286 CPU maximizes the efficiency of both the processor's instruction set and the system bus structure. iAPX 286 instructions implement extended functions that typically require many instructions. Additionally, pipelined memory access techniques further enhance processing speed by enabling the CPU to achieve higher bus bandwidth. These features result in the greatest performance while minimizing system cost by reducing the need for higher-speed memories.

## New Architecture for Simplified Software Development

The instructions of the iAPX 286 increase code density and execution speed. The iAPX 286 instruction set includes many instructions for powerful data and arithmetic manipulations, as well as enhanced high-level language code efficiency and performance. These instructions and the large address space of the iAPX 286 encourage the use of high-level languages for writing efficient operating systems and application programs.

Hardware integration of both virtual memory support and memory protection significantly reduces the software required to provide these features. Because the iAPX 286 hardware directly controls the most performance-critical functions—task switching and virtual address translation—it reduces the size of an operating system and maximizes system performance. Because the virtual memory support is an integral part of the iAPX 286 architecture, virtual memory address translation is also transparent to software.

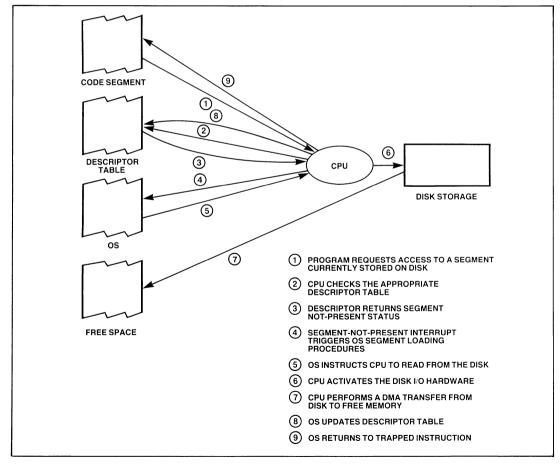

The hardware of the iAPX 286 enables the operating system to handle the program and data swapping necessary for virtual memory. When a program requests a segment which is in secondary storage (such as a disk drive), the processor initiates the operations to swap the desired information into real memory. Swapping operations are completely transparent to the application program.

iAPX 286 instructions are fully restartable to simplify returning to the application program after the completion of program and data swapping. Instruction restartability, combined with on-chip virtual memory support, greatly simplifies the tasks of both hardware and operating system software designers.

The iAPX 286 protection mechanism does even more to simplify both operating system software and applications software development. Application programs do not require special instructions to call the operating system while task switching and parameter passing to the operating system require no software overhead in the operating system.

As a result of its advanced architecture, the iAPX 286 is easy to program. The operation of the address translation and protection mechanisms is handled transparently so that application programs remain uncomplicated. Programs are smaller and cost less to develop. It is this transparency which allows the iAPX 286 to execute programs for the iAPX 86 and 88 with little or no modification, even though they were not originally written for a virtual memory system.

## FLEXIBLE HARDWARE CONFIGURATIONS

The iAPX 286 offers extensive system configuration options. The 68-pin CPU provides a full 16-megabyte address bus and a 16-bit data bus. Because the memory management and protection support is incorporated within the CPU, a protected virtual memory system may be implemented without requiring external memory management units (MMUs).

The configuration options range from singleprocessor dedicated-function systems to multiprocessor, multi-user reprogrammable systems. Specialized support circuits from Intel accommodate dynamic memory interfaces, multiprocessor environments, and CPU extensions such as the 80287 Numeric Processor Extension.

Intel provides a large selection of peripheral devices for interfacing the iAPX 286 with mass storage systems, video displays, and communications networks. You can implement memory systems with a variety of ROM, EPROM,  $E^2$ PROM and static or dynamic memories offering a range of speed and density options: The iAPX 286 also supports a Multibus<sup>TM</sup> system bus interface. Using this interface allows immediate configuration of systems with the extensive base of existing Multibus compatible memory, peripheral control, and CPU boards.

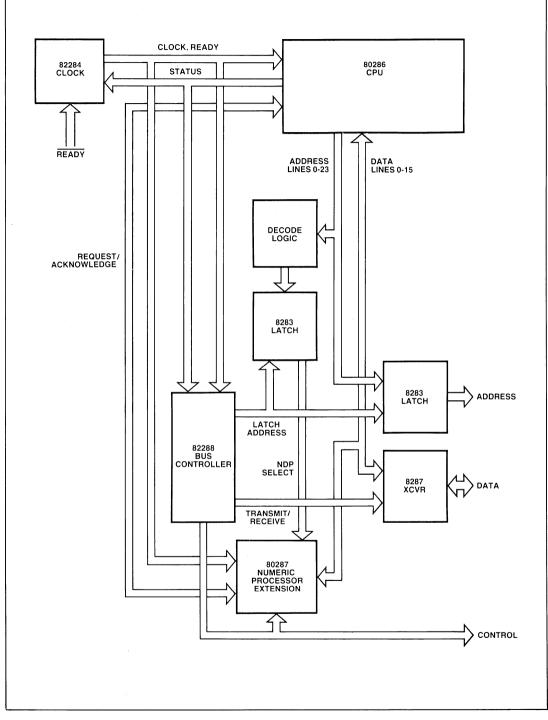

#### Numeric Data Processor

The iAPX 286/20 Numeric Data Processor configuration provides the high-speed mathematical capabilities many systems demand. Including the 80287 Numeric Processor Extension, this configuration meets the specifications of the proposed IEEE standard P754 for numeric data processing and maintains compatibility with iAPX 86/20 systems. A software emulation package is also available for lower performance systems, to execute in both Real Address and Protected Modes.

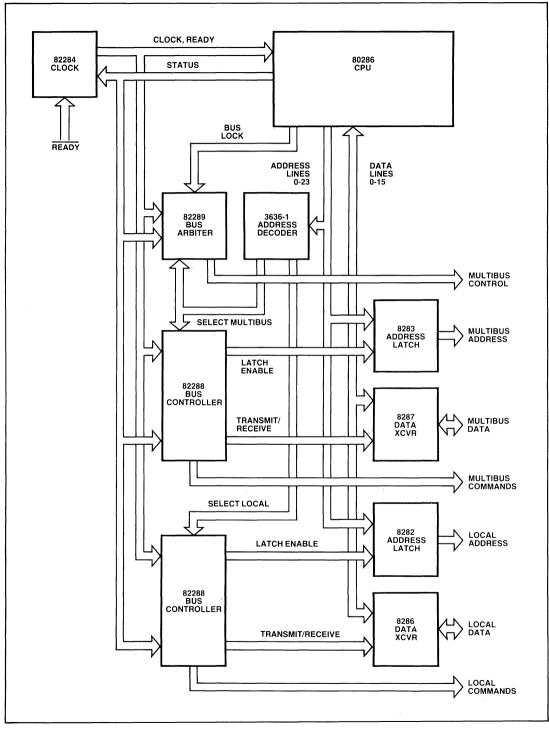

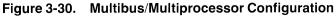

#### **Multiprocessor Capabilities**

A system designer can easily configure a multiprocessor system using the iAPX 286. The integrated memory management unit, along with special support circuits for system bus interfacing and arbitration, allows well-controlled communications on a multiprocessor bus. Bus control and arbitration support circuits provide flexible solutions for the construction of multiprocessor bus structures like the Intel Multibus (IEEE Standard 796).

#### **System Support Circuits**

Support circuits for use in iAPX 286 systems include circuits designed for bus interface, memory, and peripheral system support.

Bus interface support is provided by chips which handle tasks such as system timing, bus communications, and control. These circuits reduce the task of hardware design to the selection of the appropriate component to provide the required function. Examples of this support group are bus controllers, data transceivers, and address latches.

Intel's Advanced Dynamic RAM Controller supports a direct interface between dynamic RAM (DRAM) and the CPU of an iAPX 286 system. It also provides dual-port operation for multiprocessor systems and is compatible with Intel's 8206 Error Detection and Correction Chip (ECC) for systems requiring a high degree of data integrity.

Intel manufactures specialized controllers which provide peripheral support for dedicated system functions.

- To accommodate mass storage needs, Intel manufactures peripheral controllers for bubble memory, floppy diskette, and hard disk systems.

- Video display controllers include a range of simple to sophisticated alphanumeric displays and a graphic display control device.

- Communications controllers can manage simple asynchronous protocols as well as bitsynchronous protocols like SDLC. The communications options for the iAPX 286 will also include advanced techniques like Ethernet\* for local area network applications.

#### **Board Systems**

The iAPX 286 will be available in both component form, and as a preconfigured, pretested Multibus-based single-board computer from Intel for prototyping and for production requirements. The Multibus system bus interface not only provides multiprocessor support, but it also enables you to quickly design complete iAPX 286 systems using available board-level memory and peripheral control products. Using these support products, you can bring your products to market with minimum delay and design effort.

This full complement of system support circuits and board products enables the iAPX 286 to address a wider range of computer applications than any previous microprocessor system. Intel's broad range of modular solutions enables you to develop simple to sophisticated systems quickly and easily.

#### SAMPLE APPLICATIONS

The iAPX 286 is ideal for multi-user, real-time multitasking, and multiprocessor systems. It can support high-performance, real-time applications which have been traditionally beyond the capabilities of a microprocessor-based system. This section briefly describes a few of the potential applications for this advanced microprocessor system.

#### iAPX 86 System Upgrade

The iAPX 286 Real Address Mode enables an iAPX 286-based hardware system to use existing iAPX 86 programs without modification. The major benefits of this system migration path are:

- Total preservation of software investment

- As much as a six-fold increase in throughput

Later, as end-product requirements grow, the system software may be modified in stages to add software protection, without requiring hardware changes.

<sup>\*</sup>Ethernet is a trademark of the Xerox Corporation. The Ethernet protocol was developed jointly by DEC, Xerox, and Intel.

#### **Multi-user Systems**

The high execution speeds, total task isolation, and operating system protection make the iAPX 286 ideal for multi-user systems. The high execution speeds enable a system to handle more users with improved response time for each user. Intertask isolation protects one user's code and data from another's. Operating system protection provides total system integrity.

The iAPX 286 is ideal for multi-user business systems. The protection features can separate private financial data from word-processing or order-entry data even as the data is being processed. The virtual memory support gives each user high system availability without restricting simultaneous use of programs. Separate tasks can be created to handle slow I/O devices such as printers or modems; these tasks can run simultaneously with user service routines without degrading user response.

The iAPX 286 provides the flexibility to swap programs and data in and out of memory for virtual memory systems. This flexibility reduces the amount of real memory required to operate a large system which, in turn, reduces system cost.

#### **Real-time Multitasking Systems**

The iAPX 286 hardware task-switching support considerably reduces the time and code required to save the state of one task and load another. The multitasking capability of the iAPX 286 handles complex applications such as a large PABX system controlling thousands of lines. Distributed process control is another application which can take advantage of the multitasking and protection capabilities of the iAPX 286.

#### **Multiprocessor Systems**

Many applications can benefit from the concurrent operation of multiple processors. A typical application for multiple processors is a system with dedicated I/O processors which assume the entire burden of driving a complex I/O device. The iAPX 286 is an ideal master processor for these systems.

The iAPX 286 simplifies the design of multiprocessor configurations with hardware that supports the industry-standard Multibus structure. The iAPX 286 protection mechanism also provides support for multiprocessor communications to simplify the task of programming concurrently operating CPUs.

This interprocessor compatibility enables a system designer to construct a multiprocessor system using any members of the family. For example, an iAPX 286 CPU can serve as a master controller for a series of I/O processors (such as the Intel 8089) which, in turn, control the I/O for the system. In this type of a system, the dedicated processors remove the I/O overhead from the master CPU to increase system throughput.

## Real-time High-performance Systems

The high-speed operation of the iAPX 286 opens new doors to applications which have been neither feasible with slower microprocessor systems nor cost-effective on minicomputer systems. Higher speed operation allows you to add more features and more users without degrading system response time. Image processing, graphics, and educational computing systems are examples of real-time applications for the iAPX 286's high-speed, economical hardware.

#### DEVELOPMENT SYSTEMS AND SOFTWARE

Intel assists the system designer with assemblers, compilers, development utilities, and an in-circuit emulator for debugging which decrease both the time and the costs of producing software. From single-board computers to full hardware development systems, Intel provides an environment for the creation of extremely sophisticated microcomputer products.

#### Intellec<sup>™</sup> Microcomputer Development Systems

Intel produces the Intellec Series III Microcomputer Development System as a complete center for the development of microcomputerbased products. This system includes an iAPX 86 CPU, a hard-disk system interface with operating software, and a CRT with a 2000-character display and detachable keyboard.

In-circuit emulation (ICE<sup>m</sup>) modules and software will be available for the Series III to simplify the development of iAPX 286 hardware systems. This option enables a designer to individually develop and test software modules and then integrate them to completely isolate various system functions for testing and analysis.

Intel also manufactures the Intellec Model 675 Network Development System. This development system provides the tools to develop and test communications software and applications using Ethernet for office automation systems. An Ethernet communications controller incorporates the Ethernet Data Link and Physical Link Control to provide a 10-megabit-per-second data transmission rate over coaxial cable.

These development systems are compatible with the wide range of hardware designed for the Intel Multibus. Software compatibility among the Intel development systems enables the use of the programs described below for the rapid development of microcomputer-based products.

#### **Evaluation Software**

The Intellec Series III Development System supports an iAPX 286 Evaluation Package. This is a package of programs that enables system designers to evaluate the operation and capabilities of the iAPX 286. The Evaluation Package includes all of the tools a programmer needs to become familiar with the operation of the iAPX 286 protection mechanism and other new features. The simulator enables a programmer to gain experience by developing software modules which can later be used directly on an iAPX 286 system.

#### **Development Software**

Intel's wide range of development programs and high-level languages attests to its tradition of strong support for the development of hardware and software products. The Development Software Release for the iAPX 286 has the right mix of tools to simplify the development of all levels of software from application programs to operating systems. These tools include high-level languages, an assembler, and utilities for combining and structuring software.

The Development Software Release includes utility programs that can eliminate much of the time, effort, and expense involved in creating system software. These utilities include a binder that links modules written in different languages into a single program. This capability allows a programmer to write each module in the most efficient language, rather than having to write the entire system in a single language.

A system-building utility simplifies the generation and maintenance of operating systems. It also provides an easy means of specifying the operation of the iAPX 286 software protection mechanism. Other utilities provide run-time support for high-level languages such as Pascal and FORTRAN.

#### **High-level Languages**

High-level languages are most valuable for reducing the time and cost of program development and maintenance. Intel's efficient compilers, combined with the large address space and the high performance of the iAPX 286, encourage the use of high-level languages for the development of software. Intel's structured system language, PL/M, will be the first high-level language available for the iAPX 286. Following PL/M will be Pascal and FORTRAN.

#### SUMMARY

The iAPX 286 is a microsystem for the '80s. On increased throughput alone, the iAPX 286 is a major advancement in microprocessor technology. In addition, its extraordinary on-chip memory management support, complemented by the powerful protection mechanism, gives the iAPX 286 the ability to address applications never before served by microprocessors.

Recognizing that supplying a complete microsystem solution can reduce software costs, Intel produces software and hardware development systems that significantly simplify the program development cycle. Versatile support components from Intel simplify the creation of systems around the iAPX 286; iAPX 86-family compatibility ensures volumes of compatible software. The high performance level encourages the use of high-level languages for efficient program development. The four-level protection mechanism allows the high degree of operating system and user program integrity required of new applications. The large virtual address space and virtual memory management supports the dynamic memory demands of multi-user systems while maximizing the efficient use of real memory.

The iAPX 286 microsystem provides the framework for the development of extremely powerful products. This capability—with strong support from Intel—makes the iAPX 286 the ideal choice for applications ranging from intelligent reprogrammable workstations to complete multi-user, real-time multitasking, interactive systems. Section 3 Technical Overview of the iAPX 286

3

#### SECTION 3 TECHNICAL OVERVIEW OF THE iAPX 286

This technical overview presents the concepts governing the operation of the iAPX 286 microsystem. The discussion covers all aspects of the iAPX 286 microsystem, including the 80286 CPU as well as support devices and optional extensions.

The material in the technical overview is organized by levels of increasing detail. Readers familiar with the basic operation of the iAPX 86 or 88 may choose to begin directly with the later sections which discuss the unique attributes of the iAPX 286.

The first section describes the iAPX 286 basic programming model. This section explains the registers, data types, addressing modes, and instructions which handle most of the processing functions within the system. These features are representative of the base iAPX 286 architecture without extensions.

The second section of the technical overview describes the extended capabilities which are available with the addition of a Numeric Processor Extension to an iAPX 286 system. These capabilities include new floating-point register extensions for high-speed extended-precision arithmetic calculations.

The third section of the technical overview expands the description of the basic programming model to include features which provide special capabilities. These advanced features include special data types, enhanced instructions, special addressing modes, and protection of software.

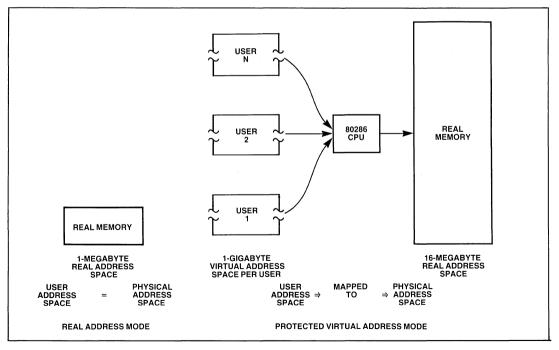

The iAPX 286 provides two modes of operation, Real Address Mode and Protected Virtual Address Mode (or Protected Mode). Both modes are compatible with the iAPX 86 and 88 CPU's so that most existing application programs can execute in either mode with little or no modifications. On power-up, the iAPX 286 begins execution in Real Address Mode and can address up to a megabyte  $(2^{20}$  bytes) of physical memory. The software may switch the CPU from Real Address Mode to Protected Mode, expanding the address space up to 16 megabytes  $(2^{24}$  bytes) of real memory within the system and up to a gigabyte  $(2^{30}$  bytes) of virtual memory per user (see Figure 3-1). This expansion in programmer visible address space is the primary difference in programs that migrate from one mode to the other.

#### **BASIC PROGRAMMING MODEL**

The basic programming model described here extends across the range of 16-bit processors from Intel. The architecture of the iAPX 86, 88, 186, and 286 simplifies programming by supporting the most commonly used data types as operands. It also provides a wide range of flexible addressing modes and a powerful instruction set.

The features described in this section apply to both modes of iAPX 286 operation. An application program written for Real Address Mode is also compatible with Protected Mode operation.

#### **Basic Register Model**

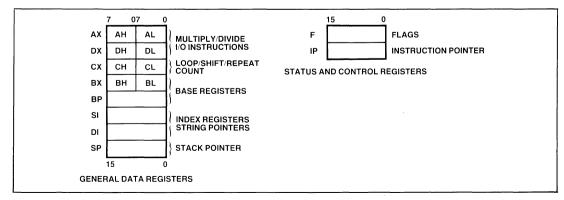

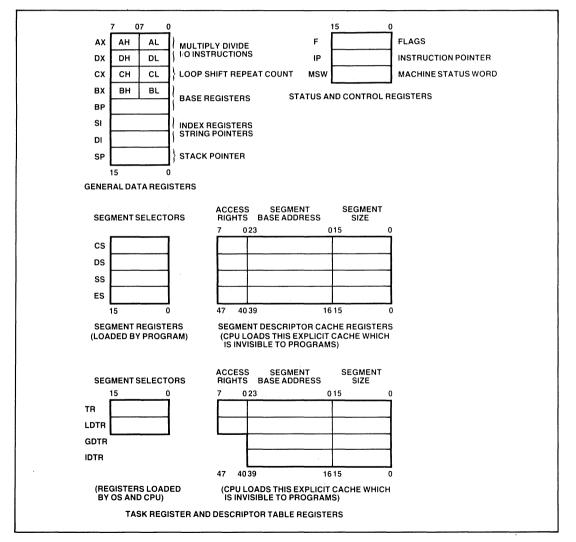

The 80286 basic register model includes the ten registers shown in Figure 3-2. The eight 16-bit general-purpose registers (AX to SP) contain arithmetic and logical operands; the two special-purpose registers reflect certain aspects of the 80286 processor state. The register set is symmetrically addressable for all basic move, arithmetic, and logical operations.

Four of the general data registers may be divided into high and low sections for manipulating byte variables. These are the AX, BX, CX, and DX registers. The corresponding eight 8-bit registers are AH, AL, BH, BL, CH, CL, DH, and DL. This allows efficient manipulation of individual bytes within words such as character manipulation within strings of data.

Not only are arithmetic and logical operations available with all general data registers, but each of these registers also handles special functions for certain instructions. To provide code efficiency, the iAPX 286 includes compact instruction encodings with implied use of general registers for these instructions. These instructions extend the base instruction set which operates on the general register set. As examples, the AX and DX registers contain operands for Multiply and Divide instructions. Additionally, the CX register can maintain a count value for automatic iteration control during the execution of software loops. The SP register in Figure 3-2 is the stack pointer. The stack pointer normally indicates the offset address for the current top of stack. Push, Pop, and other instructions implicitly refer to the stack. These instructions use SP as a destination or source operand address and automatically increment or decrement the value of SP as part of their operation.